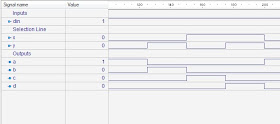

In this lecture we will learn about demultiplexer and its vhdl code.we will simulate demultiplexer using EDA Playground. What is Digital Demultiplexer (Demux)? Types of Demultiplexer 1 to 2 Demultiplexer & Truth Table? Schematic Diagram of 1 to 2 Demultiplexer using Logic Gates 1 to 4 Demultiplexer? Truth Table Schematic of 1 to 4 Demultiplexer using Logic Gates Implementation of 1 to 4 Demultiplexer Using 1 to 2 Demultiplexers 1st configuration: 2nd configuration: 1 to 8 Demultiplexer? Truth Table 1 to 8 DeMux. Build and simulate 4×1 mux, 8×1 mux, 1×4 demux and 1×8 demux in VHDL February 27, 2020 February 25, 2020 by Projugaadu 4×1 8×1 multiplexer 1×4 demux and 1×8 demux.

1X8 DEMUX VHDL source code

This page of VHDL source code covers 1X8 DEMUX vhdl code.

VHDL Code

Vhdl Demux Code

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity dmux1 is

port(f:in std_logic;

s:in std_logic_vector(2 downto 0);

y:out std_logic_vector(7 downto 0));

end demux1;

architectural behavioral of dmux1 is

begin

y(0)<=f when s='000'else'0';

y(1)<=f when s='001'else'0';

y(2)<=f when s='010'else'0';

y(3)<=f when s='011'else'0';

y(4)<=f when s='100'else'0';

y(5)<=f when s='101'else'0';

y(6)<=f when s='110'else'0';

y(7)<=f when s='111'else'0';

end behavioral;

USEFUL LINKS to VHDL CODES

Refer following as well as links mentioned on left side panel for useful VHDL codes.

D Flipflop

T Flipflop

Read Write RAM

4X1 MUX

4 bit binary counter

Radix4 Butterfly

16QAM Modulation

2bit Parallel to serial

RF and Wireless tutorials

Vhdl Component Mux

8 To 1 Multiplexer Vhdl

Share this page

Vhdl Code

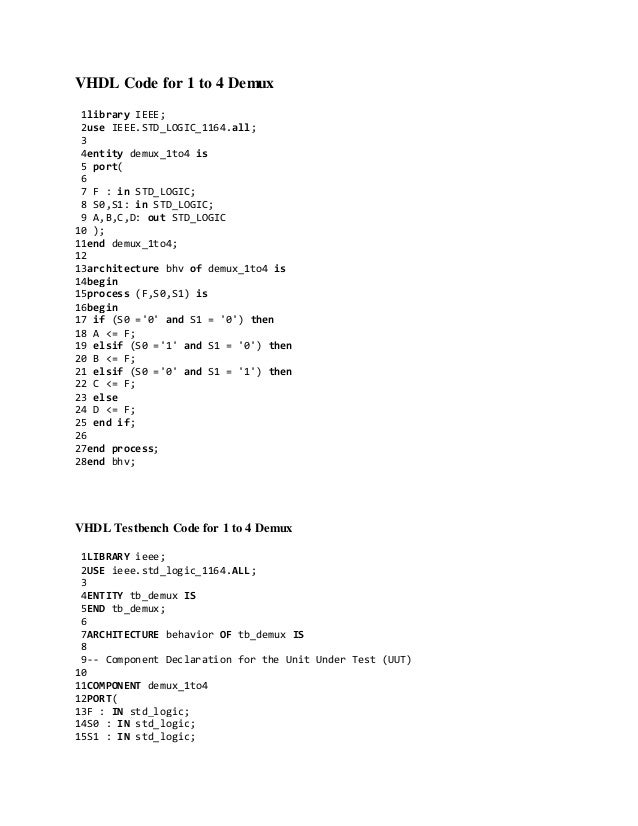

Vhdl Code For 1 To 4 Demultiplexer Using Dataflow Modelling

Translate this page